Produkte

Suchen

HDI-SBU-Multilayer

Vielschichtige Vorteile für Ihre Baugruppe

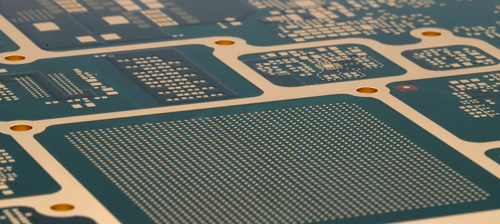

Maximale Leistung auf minimalem Raum

HDI steht für High Density Interconnect, SBU für Sequential Built Up. HDI-SBU-Multilayer sind also Leiterplatten mit ≥4 Lagen, die sequenziell in mehreren Schritten verpresst werden und in Kombination mit Micro-Vias sowie feinsten Leiterbildstrukturen hochdichte Layouts und Schaltungen ermöglichen .

Hinter dieser komplexen Bauweise verbergen sich für Sie also ganz klare Vorteile. Wir sparen Platz, wo Platz benötigt wird. Welches elektronische Gerät auch immer Sie mit uns entwickeln möchten: Sie wünschen oder benötigen vermutlich die maximale Funktionalität, kostenoptimiert auf minimalem Raum? Oder Sie verwenden moderne, hochpolige aktive Bauelemente mit kleinstem Pitch? Genau das ermöglichen unsere HDI-SBU-Multilayer durch ihre besonders kompakte Gestaltung.

Wie das realisiert wird? Komplexe HDI-SBU-Multilayer von CONTAG ermöglichen durch eine gezielte Kombination verschiedenster technologischer Features die erforderliche Integrationsdichte. Dazu gehören neben dem sequentiellen Pressaufbau insbesondere die Reduzierung der Leiterbildstrukturen auf ≤100µm, Mikrobohrungen ≤200µm als Blind- und Buried Vias sowie Fülltechnologien für die Micro Vias. All dies schafft den gewünschten, eng gepackten Bestückungsraum auf den Außenlagen, gerade auch in Kombination mit Fine-Pitch BGAs oder CSPs der neuesten Generation.

Vorteile von HDI-SBU-Multilayern

- Maximale Performance auf minimalem Raum:

- Höchste Packungsdichten, Platzausnutzung und Miniaturisierung der Baugruppe

- Maximale Freiheiten in der Bauteilplatzierung

- Verkürzung der Leiterbahnlängen auf der PCB

- Verbesserung des EMV-Verhaltens

- Verringerung störender Induktivitäts- und Kapazitätseffekte

- Verbesserte Signalintegrität bei High-Speed-Designs - Kostenreduzierung durch Reduzierung der Lagenzahl

- Vereinfachte Entflechtung des PCB-Layouts

- Höhere Zuverlässigkeit durch HDI-Leiterplatten aufgrund der hohen thermischen Belastbarkeit gefüllter Micro Vias und moderner Harzsysteme

CONTAG Ihr Kompetenzcenter für HDI-SBU-Multilayer

Vielschichtige Vorteile in komprimierter Form: HDI-SBU-Multilayer bringen das Beste für Sie zusammen.

CONTAG zählt im Bereich der HDI-SBU-Multilayer zu den marktführenden Unternehmen in Europa. Mit einer jahrelangen Expertise in der Design- und Konstruktionsberatung sowie Fertigung der gesamten technologischen Bandbreite dieses Schaltungstyps können wir Ihnen immer das bestmögliche Ergebnis in schnellstmöglicher Zeit liefern. Express ist unser Standard und wir sind erst dann zufrieden, wenn Sie glücklich sind. Wie wir das möglich machen? Mit einem spezialisierten Team, das mit ganzem Know-Wow und voller Leidenschaft in drei Schichten jederzeit für Sie da ist. Mit einer High-Tech-Produktion made in Germany, direkt bei uns vor Ort in Berlin.

Anwendung

HDI-SBU-Multilayer sind die optimale Lösung für alle elektronischen Baugruppen und Geräte, deren kompakte Bauweisen ein Höchstmaß an Miniaturisierung und Komprimierung erfordern. Mit der zunehmenden Digitalisierung und Trends wie IoT (Internet oft hings), Industrie 4,0, KI, Elektromobilität, etc. finden sich in nahezu allen Branchen zunehmend Anwendungen für diese komplexen Boards.

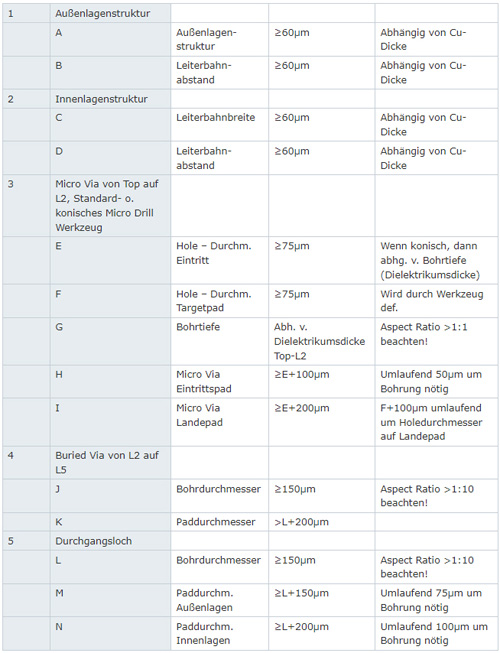

Design Guide

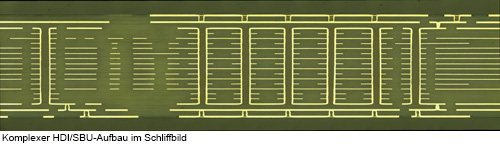

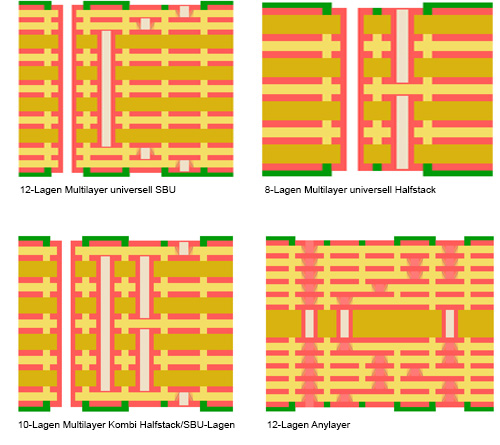

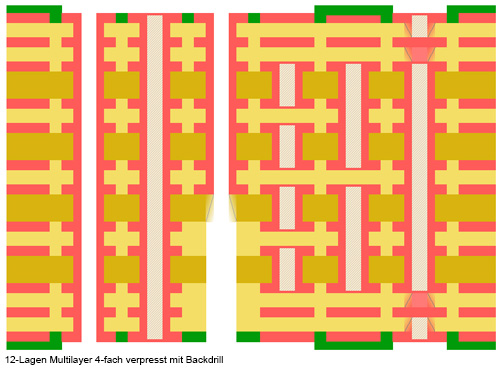

Die Aufbauvarianten von SBU-Multilayern sind extrem vielfältig. Gemeinsames technologisches Merkmal ist, dass mindestens 2 Pressschritte benötigt werden. In komplexeren Aufbauten können auch deutlich mehr Pressschritte erforderlich sein.

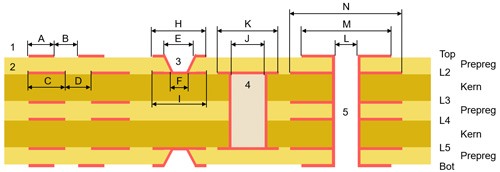

Beispielaufbau komplexer SBU

Entscheidende Kostenfaktoren beim SBU-Aufbau

- Anzahl der Pressungen

- Anzahl der Bohrprogramme und Anzahl der Bohrungen (Blind- und Buried Vias, Through Holes)

- Anzahl der Durchkontaktierungsprozesse

- Umfang der erforderlichen Verfüllprozesse (Pluggen, Cu-Filling)

- Strukturweiten (Line/Space)

Wir verarbeiten standardmäßig das phenolisch gehärtete, gefüllte Mid-Tg (ca. 150°C) Epoxydharzsystem R-1755M von Panasonic. Dieses Material ist dimensionsstabil, thermisch belastbar und für Mehrfachverpressungen geeignet. Alternativen dazu sind verfügbar und etabliert: Für Hoch-Tg-Anforderungen empfehlen wir EM-827, für High Speed Applikationen sind beispielsweise Megtron 6/7 und die verschiedenen Rogers-Materialien geeignete Alternativen. Diese Materialien stehen in vielfältigen Varianten mit unterschiedlichen Dicken und Kupferauflagen im Lager zur Verfügung. Sequentielle Lagen werden, je nach Durchmesser der Blind Vias, standardmäßig mit 2x106er oder 1x1080er Prepregs aufgebaut.

Micro Vias

Während Through Holes und spätere Buried Vias mit Durchmessern ≥0,15mm ausschließlich mechanisch eingebracht werden, werden Blind Vias sowie der Großteil der späteren Buried Vias mit Durchmessern <0,15mm hauptsächlich mit dem Laser erzeugt. Dieses Verfahren ist wirtschaftlich und ermöglicht die prozesssichere Kontaktierung auch bei engsten Lagenabständen. Oftmals werden Buried Vias als Blind Vias gebohrt und metallisiert. Wird auf die Lage eine weitere Lage aufgebaut (sequentiell build up ), werden diese Blind Vias dann zu Buried Vias.

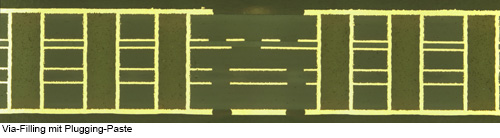

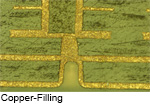

Fülltechnologien

Bei der sog. Via-in-Pad-Technologie, aber auch bei Stacked Via-Konstruktionen, bei denen die Blind Vias direkt übereinander aufgestapelt werden, müssen die Vias verfüllt und mit einem Kupferdeckel versehen werden. Als universelles Füllverfahren für Through Holes und Blind Vias hat sich das Via Filling mit einer sog. Plugging-Paste aus Epoxydharz etabliert. Mit Vakuumunterstützung wird die Paste in die Bohrungen gedrückt, ausgehärtet und dann mittels Schleifverfahren auf der Oberfläche eingeebnet. Bei einer anschließenden Metallisierung wird ein Kupferdeckel aufgebracht.

Oft kommen bei der Fertigung eines komplexen Aufbaus auch beide Verfahren zum Einsatz.

Qualitätssicherung

Für eine zuverlässige und qualitativ hochwertige Fertigung werden die kritischen Fertigungsschritte durch prozess- und auftragsbezogene Einricht- und Schliffuntersuchungen überwacht.

Die relevanten, produktbezogenen Qualitätsparameter sind hierbei

- Anbindungszuverlässigkeit (Bohrtiefe) der Blind Vias

- Cu-Schichtdicke in den Buried Vias (>15µm spezifiziert)

- Cu-Schichtdicke in den Blind Vias (>20µm spezifiziert)

- Registrierung (Treffgenauigkeit) der Blind- und Buried Vias auf den Innenlagen, Restringe gemäß IPC

- Dickengenauigkeit- und Verteilung nach den Pressvorgängen

Sie wünschen sich weitere Tipps und Hinweise für Ihr Layout?

Die Technologien entwickeln sich kontinuierlich weiter. Zur aktuellen Machbarkeit wenden Sie sich gerne an das CONTAG-Team.

Ihr direkter Draht

+49 30 351 788 -333

team contag.de

contag.de

Anfrage, Bestellung

Anfrage, Bestellung